© 1999-2023 Jürgen Müller

juergen@e-basteln.de

The 6502 was the CPU in my first computer (an Apple II plus), as well as many other popular home computers of the late 1970s and 80s. It lived on well into the 1990s in game consoles and chess computers, mostly in its updated “65C02” CMOS version. Here’s a re-implementation of the 65C02 in an FPGA, in a pin-compatible format that lets you upgrade those old computers and games to 100 MHz clock rate!

The idea of implementing a CPU core inside an FPGA is not new, of course. In fact, the CPU core I am using is not my own, but was developed as a 6502 core by Arlet Ottens, and extended to cover the 65C02 opcodes by Ed Spittles and David Banks. A big thank-you to Arlet, Ed, and Dave for developing the core and sharing it freely! Links to their original work are on the Files & Links page.

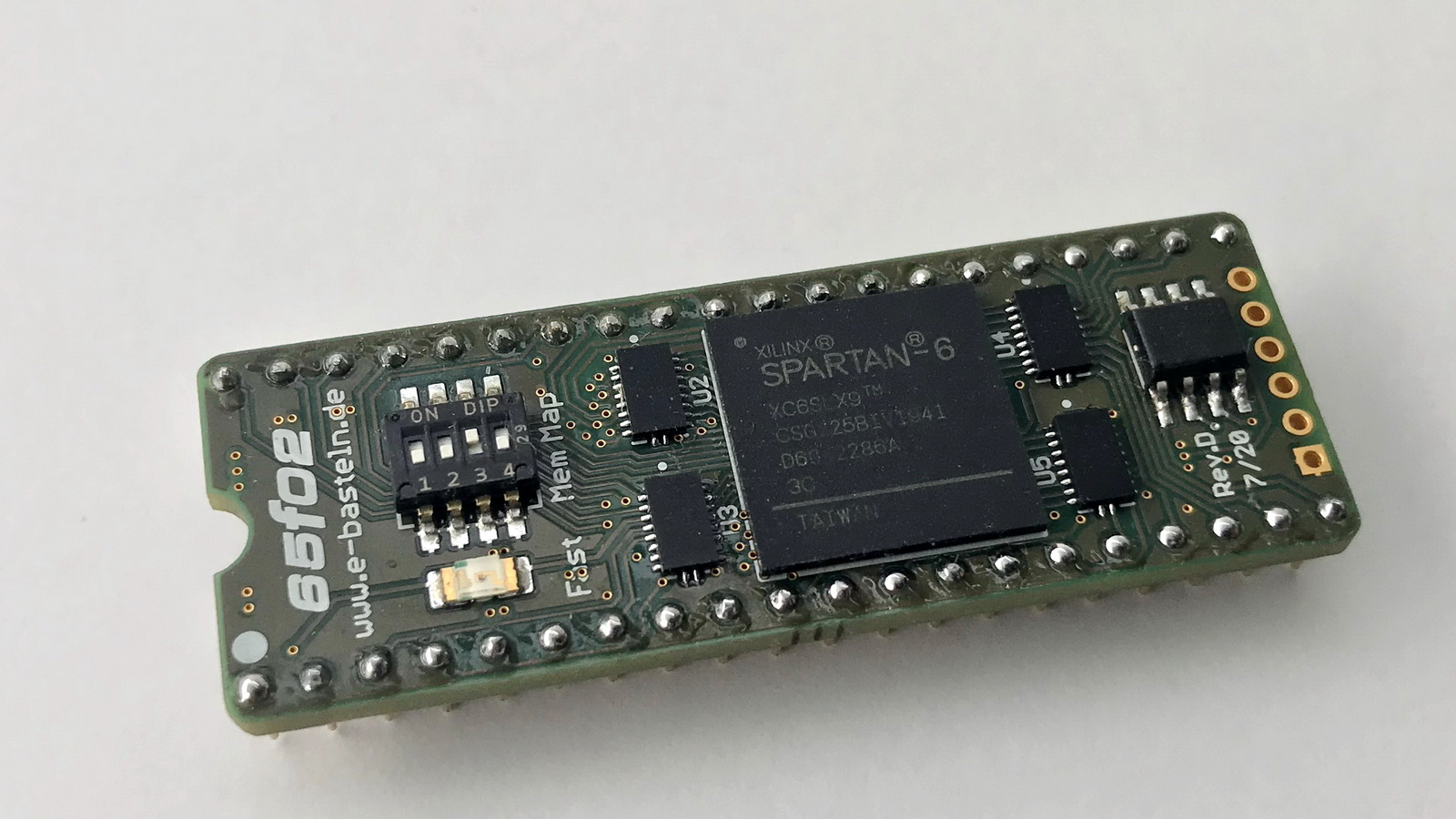

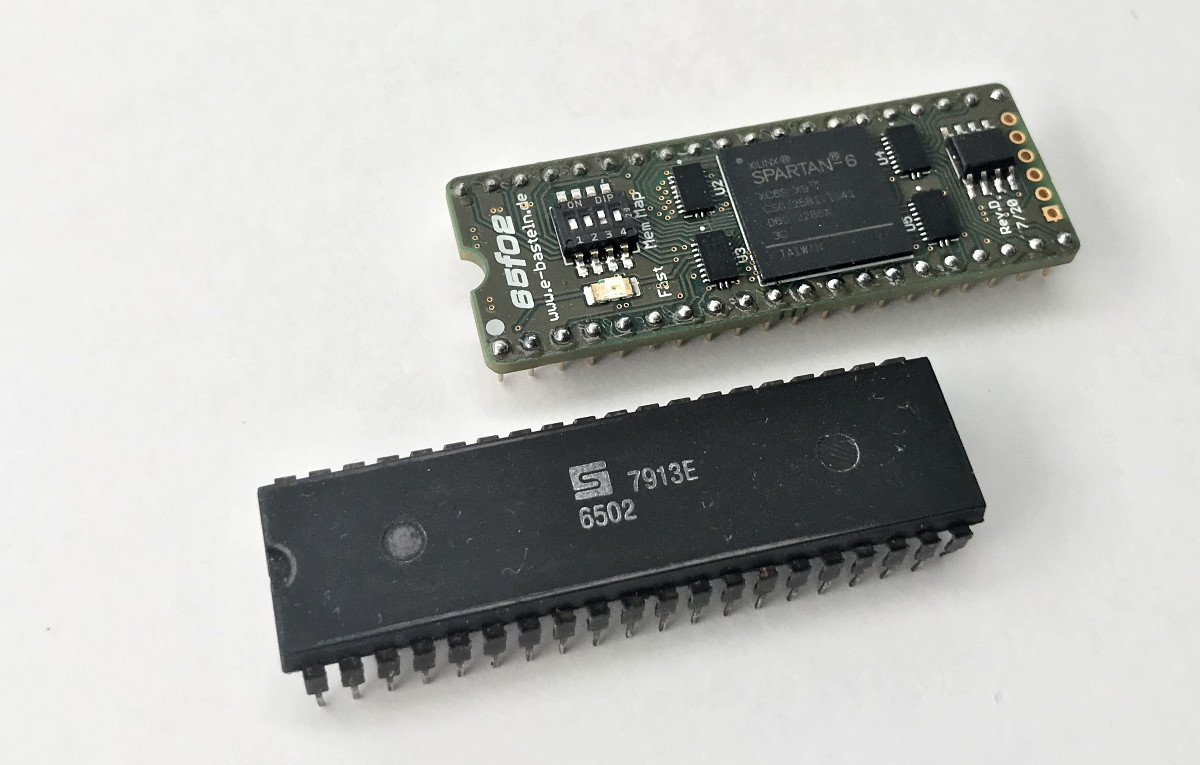

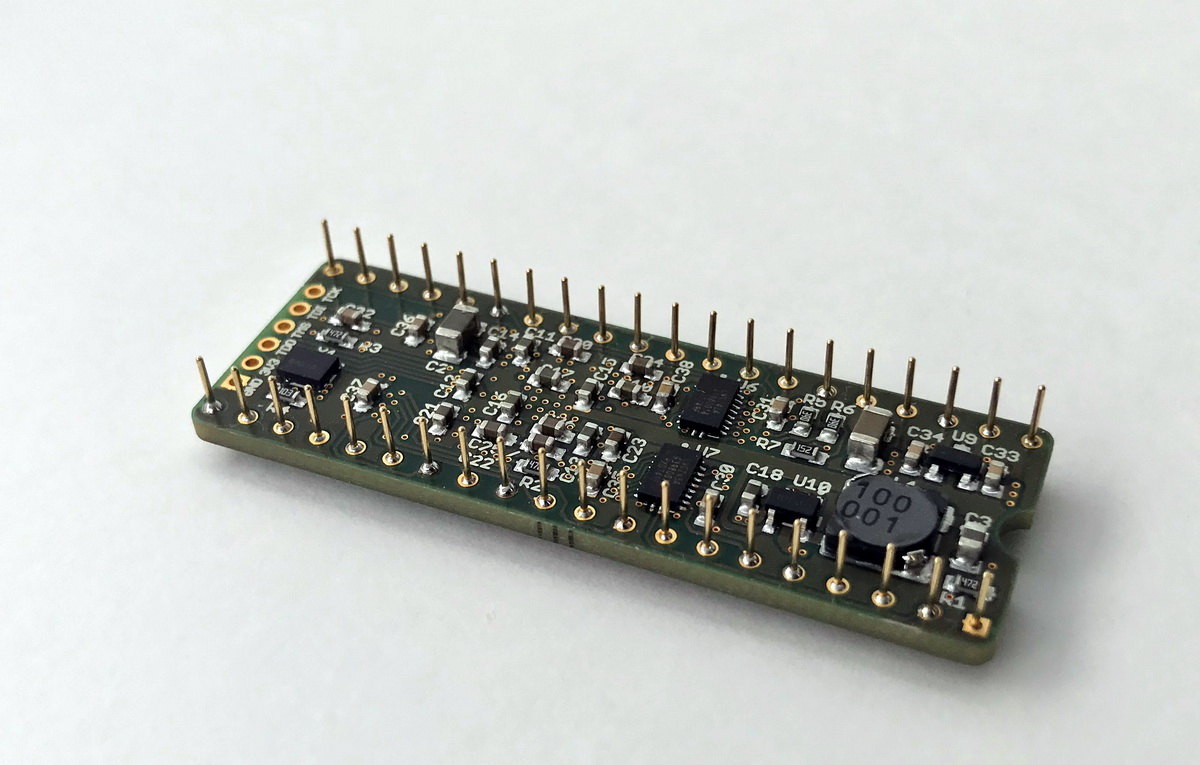

I packaged this in a Spartan-6 FPGA (with 64 kByte on-chip RAM), on a small circuit board which is just the size of a 40-pin dual inline package, with pins matching the 65C02 pinout. I added logic inside the FPGA which can access the external 65C02 bus with the correct timing, based on whatever clock is coming in from the host system. Inside the FPGA, the CPU core runs at 100 MHz. I dubbed this the “65F02”, where the “F” might stand for FPGA or for “Fast”. ;-)

The 65F02 circuit board: same footprint and pinout as the original 6502 and 65C02 CPU.

The idea is to use this as a “universal” accelerator for 6502 and 65C02-based host computers – just plug it into the CPU socket. The only thing the FPGA board needs to know about its host is the memory map: Where does the host have memory-mapped I/O? Up to 16 different memory maps can be stored in the FPGA, and selected via a mini DIP switch. Upon power-on, the 65F02 grabs the complete RAM and ROM content from the host and copies it into the on-chip RAM, except for the I/O area. Then the CPU gets going, using the internal memory at 100 MHz for all bus accesses except for any I/O addresses – for these, the internal CPU pauses, and an external bus cycle is started at whatever the external clock speed is.

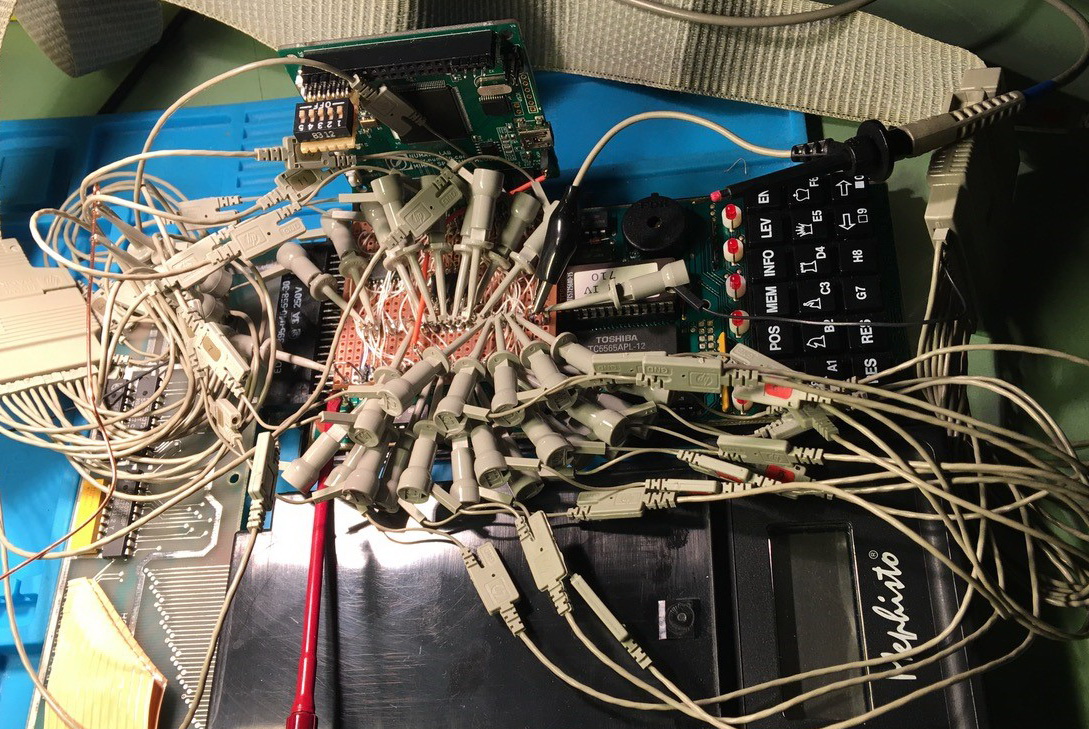

Kudos to Roland Langfeld, who suggested this elegant way of integrating an accelerator into almost any host, and has contributed a lot during the testing and debugging effort. Roland’s original interest was in 6502-based chess computers (there were some really nice ones in the 1980s). But we have successfully tested the prototype 65F02s in an Apple II and a Commodore 8032, as well as various chess computers.

Thanks go to Roland Langfeld, for the idea for the 65F02 and many hours of debugging and testing in Mephisto chess computers and the Commodore 8032.

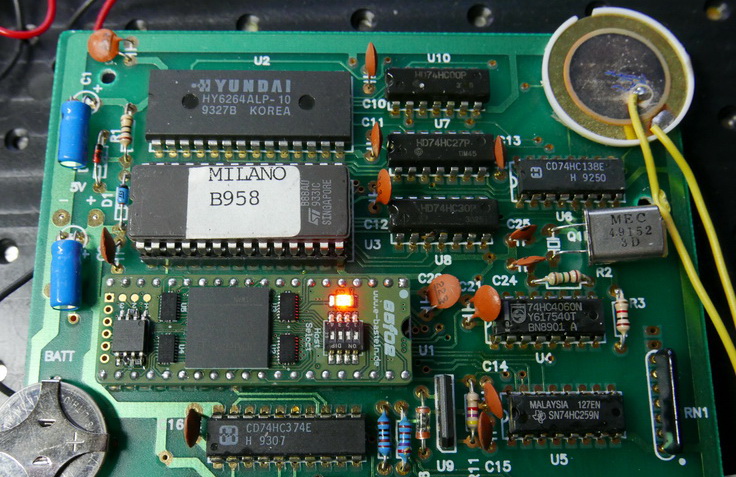

The first compact 65F02 installed in a Mephisto Milano chess computer. The populated circuit board is less than a millimeter higher than the original chip package, hence also fits into tight enclosures.

We have focused on Mephisto chess computers first, since these are at the center of Roland’s collector’s interest. But many others are on the wishlist, including Fidelity (Elite A/S Budapest and Glasgow, Prestige, Avantgarde), Novag (Super Constellation, Super Expert C), SciSys (Turbostar), …

So far, we are supporting the two 6502-based members of the classic 1977 “Trinity” of home computers – the Apple II and the Commodore PET series. It may be possible and worthwhile to also support some slightly later machines: The Acorn BBC Micro, Atari 400 and 800, and maybe the Commodore C64 come to mind. I don’t have any of these computers though. Please contact me if you are interested to help with an adaptation of the 65F02!

Apple II, including the II plus and europlus, and presumably the //e. Quite a bit of hardware and software trickery by Steve Wozniak, and the older models do not support a real 65C02 – but the 65F02 is a bit more generous in its bus timing and works nicely. The Disk II floppy drive works nicely under DOS 3.3; support for the language card is under development.

Commodore PET/CBM up to 8032. A very clean and “by the book” design. The same memory map should work for all models from the PET 2001, the 3000 and 4000 series, and the 8000 series up to the 8032. (But excluding the 8096 and beyond, which require memory bank switching.) So far we have tested this on the 8032 only; the 8050 floppy drive works.

A caveat is in order here. The home computers, with their flexibility and expandability on both the hardware and software side, are bound to encounter limitations and incompatibilities:

Memory expansion boards and bank switching need to be known to and emulated by the 65F02; and since the 65F02 only has 64 kByte of RAM on board, it cannot fully accelerate the extended memory. Also, while the 65F02 makes an effort to detect the access to time-critical peripheral devices, and switch back to the original slow speed temporarily, there will probably be incompatible software or add-on hardware. And finally, some software you simply don’t want to be accelerated – try an action video game at 100 MHz to understand that concern…

The 65F02 supports an optional hardware switch to disable the acceleration. This way, one can still select between accelerated operation and original speed before one starts the host computer. In non-accelerated mode, the 65F02 should be fully compatible with any software or add-on hardware. (Well; unless the software uses undocumented 6502 opcodes…)

This is a hobby project, and I have no plans at the moment to take it commercial.

Several of the small-form-factor PCBs have been assembled, and have been successfully tested in the above-mentioned computers. The tested computers include environments with TTL and CMOS logic levels, and clock rates ranging from 1 to 5 MHz. IRQs and NMIs are used in the hosts; some of the Mephisto chess computers actively use the READY signal to slow down the CPU, and the 65F02 respects that nicely. We have not used the SO (set overflow) input in earnest, but believe it to work.

The chess computer community has put the 65F02 through its paces and found some very nice improvements in playing strength for the old chess computers. Games and commentary can be found in the German schachcomputer.info forum, in particular in the threads here, here, and here.

If you have ideas for the 65F02, would like to help in developing support for additional computers, would like to write about it, please contact me via the email address provided in the About section.

Update, July 2022: The global electronics supply bottlenecks affect this project too. The Xilinx Spartan-6 FPGA (in the required package and speed grade) has moved from a lead time of more than one year to “we don’t know”. The 65F02 will sit on the back burner until the supply situation hopefully returns to normal.

The 65F02 can directly replace a 6502 or 65C02 in their 40-pin DIP socket.

The bottom side of the circuit board. Left to right: clock oscillator, decoupling capacitors, level converters for 5V input signals, voltage regulators.